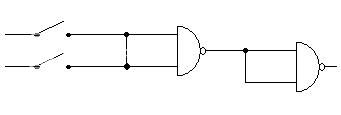

또는 2 개의 NANDS를 사용한 게이트 [폐쇄

-

19-09-2019 - |

문제

NAND 게이트에서 OR 게이트를 만들기 위해 본 다이어그램은 3 NAND 게이트를 사용하지만 두 번째 NAND 게이트의 두 커넥터에 입력 한이 게이트의 출력으로 두 입력이 연결되어있는 경우 두 입력이 두 번째로 연결됩니다. 그것은 또는 문처럼 행동해야합니다. 그래서 당신은 단지 2 개의 게이트 만 필요합니까?

편집 : 아래 그림은 Richardbowles 사이트에서 한 시도로 인해 효과가 있다고 생각하게되었습니다. 나는 OR 게이트를 사용하여 허용되지 않은 연결을 시도하고 만듭니다. 나는 이것이 쓰레기라는 것을 깨달았다.

해결책

두 입력 모두 NAND 게이트의 두 입력에 연결 되었습니까? 이것은 두 입력 사이의 단락처럼 들립니다.

결국 당신은 그런 종류의 "또는 게이트"에 대한 게이트가 필요하지 않습니다.

실제로 NAND의 입력을 연결하면 NOT가 발생합니다. 그리고 순서대로 두 가지를 갖는 것은 ID입니다. 그것은 아무것도하지 않습니다 (논리적 인 방식으로만이 구조물을 다른 것들에 사용할 수 있습니다).

문제는 OP의 생각의 기차가 그림에서 그린 스위치만으로 작동한다는 것입니다. 디지털 전자 장치에서는 높음 (예 : +5V) 또는 낮음 (GND, 0V)으로 신호가 있습니다. 그리고 당신은 그들 사이에 아무 것도없이 두 가지 신호를 연결할 수 없습니다.

다른 팁

게시 한 사진이 전적으로 정확하지 않습니다. 그것은 그리고 게이트 역할을해야합니다. 두 번째 NAND 게이트가 인버터 역할을하여 첫 번째 게이트를 부정하기 때문입니다.

Demorgan의 정리 때문에, 또는 게이트는 3 개의 NAND 게이트로 만들어야합니다.

편집하다: 그들 사이의 연결을 보지 못했습니다. 그렇습니다. 그것은 똑같은 문처럼 행동 할 것입니다. 흥미로운 찾기.

두 입력이 A와 B라고 가정합니다. 입력 A가 높을 때 NAND의 입력이 모두 높아서 첫 번째 NAND의 출력이 낮습니다. 두 번째 NAND는 그 점을 뒤집어 높습니다.

B가 높거나 둘 다 높은 경우에도 마찬가지입니다. 두 입력이 낮 으면 낮게 반환됩니다.

이중 편집 : 그러나 전압이 a = 5V이고 b = 접지라고 말하면 A는지면으로 바로 흐릅니다. 이것이 Demorgan의 정리를 사용한 표준 접근법이 사용되는 이유입니다.

마치 당신이 앤 게이트의 구성을 설명하는 것처럼 들립니다. 편집 : 지금 당신의 다이어그램을 볼 수 있고 거기에서 무슨 일이 일어나고 있는지 볼 수 없습니다. 실제로이 회로를 만들었습니까?

네 가지 기본 패턴이 있습니다.

- 입력 또는 출력을 반전시키지 마십시오 (O = A NAND B) 결과 : A NAND B

- 출력 만 반전

- 입력 만 반전

- 입력과 출력을 모두 반전

이 디자인을 사용하면 Nands가 전혀 필요하지 않습니다. 그러나 이러한 종류의 추상화에서 두 개의 입력 신호를 직접 연결할 수 없습니다 (기본적으로 I1 == I2라고 말합니다. 전자 장치에서는 단락이 발생합니다.

OPS 솔루션은 회로에 오픈 컬렉터 입력이있는 한 (또는 MOS 기술에서 등가를 호출하는 모든 것을 사용하는 한), 풀다운 저항이 필요하도록 만들어집니다.

그러나이 경우 게이트가 전혀 필요하지 않은 경우 출력을 함께 연결하십시오.